东莞市宇熙精密连接器有限公司

关注宇熙抖音

13556645970

许多先进的系统具有多个数字接口,但现代电子设备小型化要求在连接器中整合信号。高密度连接器可以支持将信号、电源和接地整合到单个引脚中。当我们在连接器方面提到“高密度”时,我们不仅仅是在谈论信号数量。这些连接器每单位面积的引脚数往往很高,并且它们的焊盘图案开始看起来更像 BGA,而不是典型的连接器。

为了帮助系统设计人员使用这些连接器,本文将概述如何使用高密度连接器以及如何成功地布线,重点包括三个注意事项:引出线设计、布线通道设计和扇出。

为了适应高信号数量,高密度连接器将引脚封装成细间距排列。这些连接器可能有数百个引脚。在机械设计和外形尺寸方面,它们有两个共同的规格:

Samtec的一个高密度连接器示例如下所示。该连接器将高引脚数打包成多排,下面显示的特定型号 (NVAM) 支持高达 112G PAM4 信号(基于奈奎斯特频率的 28 GHz 带宽)。

用于高速信号的高密度表面贴装连接器组件。

考虑到这些要点,让我们看看一些设计策略,以支持高速 PCB上的这些连接器。

高密度连接器上的引脚通常需要支持高速和低速接口的混合。通常将较慢的协议(SPI等)和 GPIO 放在同一个高密度连接器上,作为高速接口的一组差分信号。这些引脚需要设计成使用多个接地引脚来抑制信号之间的串扰。通过交错接地引脚,可以在信号引脚之间提供屏蔽。

接下来,应将每个差分对的差分引脚组合在一起并交错排列,以允许交错的接地引脚。这允许在连接器主体下方创建布线通道。一个例子如下所示。

示例引脚排列显示在 1.27 毫米(50 密耳)引脚间距高密度连接器中与接地(白色)和差分引脚(黑色)交错。

使用此引脚排列,可以将迹线作为单条迹线或作为紧密间隔的对布线到连接器区域,具体取决于引脚间距和层数。这就是走线设计和扇出变得重要的地方,以确保走线可以在引脚之间布线,同时遵守制造间隙。

为了支持内部/背面层的布线,需要一种扇出方法来到达内部行上的所有引脚并提供布线访问。在用于板对板堆叠的高密度 SMD 连接器中,SMD 焊盘间距可以足够小(1 毫米或更小),可以与 BGA 焊盘图案相媲美。使用通孔连接器,由于着陆垫和钻孔周围环形环的尺寸,将拥有更小的空间。Dog bone扇出适用于高密度连接器,因为这将提供访问内部/背面层的通路。

为到达内部引脚而设计的布线通道可能需要非常窄的走线才能安装在引脚列之间。对于差分对,需要遵循一定的流程来确定是否可以在引脚列之间放置走线:

l 首先,选择允许细迹线的叠层,以便可以在连接器焊盘图案中到达内部的引脚行。

l 如果布线通道足够宽,则选择差分对中走线之间的小间距并确定走线宽度。

l 如果间距非常细,则在差分对之间设置较宽的间距,并设计走线以匹配目标特性阻抗。

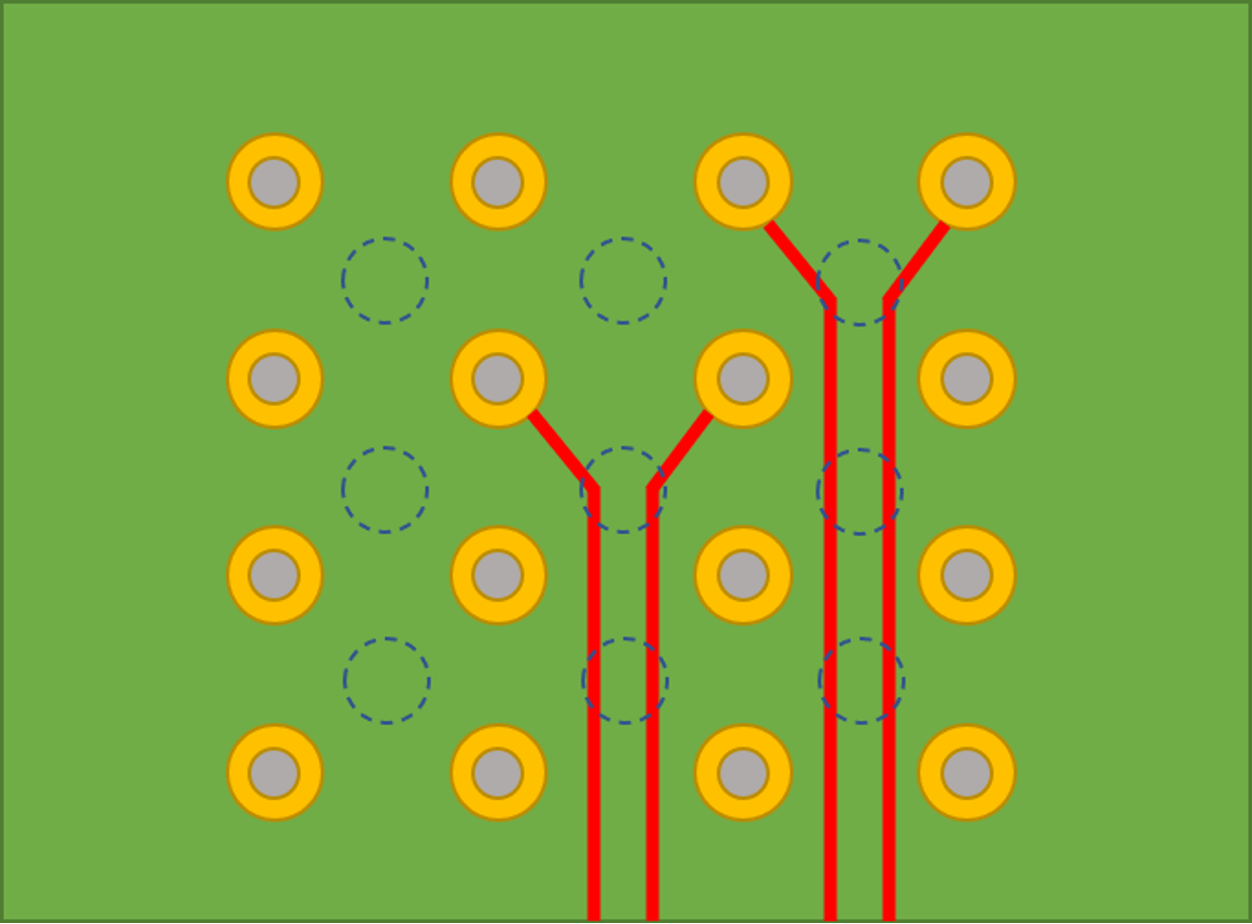

此图显示了差分对布线到内部层上的过孔。虚线圆圈显示顶层的连接器安装垫。在这种情况下,通孔通过Dog bone扇出来访问。

在内部层上走线要求信号和地之间的电介质更薄。当使用大量引脚时,内层布线的高密度连接器可能使用超过 4 层,这将迫使电介质更薄。由于走线和内部层接地之间的电介质更薄,带状线差分对布线将允许更细的走线,这些走线通常可以穿过连接器扇出中的过孔列。

当需要在 PCB 布局中放置和布线高密度连接器时,可以设计和验证的确保使用最好的系统分析工具集来验证的系统的各个级别。

Cadence的系统分析实用程序可帮助评估各个级别的设计,从前端原理图捕获到后端仿真和验证。只有 Cadence 为任何应用和任何复杂程度提供一整套电路、IC 和 PCB 设计工具。